Prozessorgeflüster (XL)

Von Medien und Meditationen

Während sich Intel auf dem IDF in San Francisco auf ein paar wenige Neuigkeiten zum ehemaligen Zentralthema Prozessoren beschränkte, konnte AMD mit einem Konter-Event die internationale Aufmerksamkeit auf sich ziehen. Mehr zu Zen, ARMv8, Parker, Power9 … folgte dann auf der anschließenden Hot-Chips-Konferenz in Cupertino.

Auf dem IDF verteilte Intel an ausgewählte Medienvertreter nur arg spärlich News zu Kaby Lake (S. 28) und die auch noch verschlossen unter „Non Disclosure Agreement“. Lediglich zum verbesserten Herstellungsprozess 14 nm+ gab es eine öffentliche Präsentation, die wie üblich Herstellungsleiter Mark Bohr abhielt. Gut 12 Prozent mehr Performance soll der Prozess mit dem Plus gegenüber dem alten 14-nm-Prozess einbringen. Nutznießer werden die Chips 2017 sein, zunächst der Kaby-Lake. Für Nachfolger Coffee Lake ist eine weitere Optimierung vorgesehen.

Bohr berichtete auch über den Stand der nächsten Prozesstechniken, die sich ein wenig verspäten werden und die inzwischen auch für längere Laufzeiten mit mehreren Updates gedacht sind. Der 10-nm-Prozess wird definitiv noch keine Extreme UV-Technik (EUV) verwenden, sondern weiterhin mit 193-nm-Lasern und Immersionstechnik arbeiten. Ab Ende 2017 sollen die ersten Chips darin gefertigt werden, etwa Cannon Lake und Xeon Phi Knights Hill.

Hier sind dann im weiteren Verlauf 10 nm+ und 10 nm++ eingeplant mit den zugehörigen Prozessoren Ice Lake und Tiger Lake.

Auch der vor einigen Jahren noch für 2017, inzwischen auf etwa 2020 verschobene 7-nm-Prozess ist, mit welchen Zaubertricks auch immer, noch für 193-nm-Immersion ausgelegt. Sollte jedoch bis dahin EUV ausgereift und insbesondere kosteneffizient sein, so könne man laut Bohr einzelne Layer auch damit herstellen.

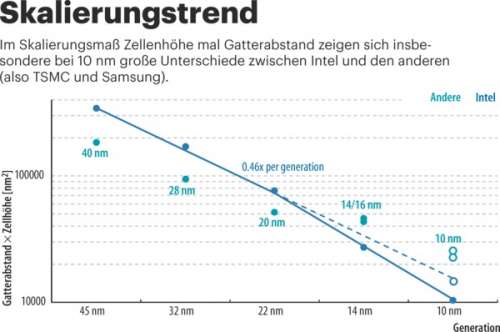

Mit Blick auf die bei 10 nm vorauseilende TSMC- und Samsung-Konkurrenz wies Bohr darauf hin, dass „10 nm“ eben nicht gleich „10 nm“ sei. Vergleicht man die tatsächlichen Strukturgrößen, wie Gatterabstand (Gate Pitch) und Zellhöhe, so sei Intel bei gleicher Bezeichnung für den Technologieknoten eine ganze Generation voraus.

Die wohl wichtigste Meldung kam jedoch aus dem Bereich der Auftragsfertigung. Intel hat sich mit ARM geeinigt und bietet deren ARM Artisan Physical IP für die Fertigung in 10 nm für zukünftige mobile ARMv8-Chips an. Erster bekannt gegebener Kunde ist LG Electronics.

Ansonsten gab es noch eine zarte Andeutung auf einen neuen Prozessor. Datacenter-Chefin Diane Bryant kündigte einen speziell optimierten Xeon Phi für Deep Learning namens Knights Mill für Ende 2017 an. Das ist nicht etwa eine Variante vom geplanten Knights Hill in 10 nm, der, wie man schon vorab auf der ISC16 hinter den Kulissen erfahren konnte, mit 88 physischen Kernen gar nicht so viel mehr Kerne haben wird wie Knights Landing. Vielmehr opfert man bei einem Knights Landing einen Großteil der für Double Precision vorgesehenen Hardware und widmet diese für Single und vor allem für Half Precision (FP16) um. Hinzu kommen noch einige neue für Deep-Learning-Algorithmen optimierte Instruktionen. Double Precision geht dann zur Not auch noch, aber da müssen sich dann mehrere Kerne eine DP-Einheit teilen.

Meditative Versenkung

Weit mehr Aufmerksamkeit konnte diesmal jedoch wenige Stunden später die andere Top-Lady im Prozessor-Business auf einer Konkurrenzveranstaltung nur einen Steinwurf weit weg vom Moscone Center auf sich ziehen. Nicht im Pariser Chic, sondern in lässiger Freizeitkleidung zeigte sich AMDs Chefin Lisa Su so entspannt wie noch nie.

Zusammen mit CTO Mark Papermaster präsentierte sie eine Palette neuer Systeme vom Notebook bis zum Server, alle bestückt mit Zen-Prozessoren. Eigentlich waren tiefere Einblicke in diese neue Prozessorgeneration für die Präsentation auf der Hot-Chips-Konferenz gedacht. Aber man konnte sich vor Freude nicht zurückhalten und plauderte schon mal vieles davon aus.

Das prinzipielle Innenleben der ersten Zen-Implementierung namens Summit Ridge haben Experten wie Chip-Architekt Hans de Vries schon im Mai mit Adleraugen aus dem Wafer-Photo ausgelesen, das bei einem Investoren-Treffen mal kurz im Video auftauchte. Darauf erahnt man die beiden CPU-Module (die heißen jetzt CCX) auf dem Chip mit jeweils vier Kernen mit je 512 KByte L2-Cache. In der Mitte ist der gemeinsame L3-Cache mit 8 MByte. Er wird per Interleave angesprochen, sodass die mittlere Latenz für Zugriffe immer gleich ist.

Jedem Modul steht ein DDR4-Speichercontroller zu Seite – zu den Memory-Controllern gibt es jedoch noch kein offizielles AMD-Statement. Auf dem Chip befindet sich noch eine I/O-Schnittstelle mit 32 PCIe-3.0-Lanes sowie zwei GMI-Interfaces – AMDs Gegenstück zu Intels DMI. Die sprechen den Pomontory-Chipsatz an.

Irgendwo müssen auch noch die Interfaces versteckt sein, die für den Datenverkehr zwischen den beiden CPU-Modulen und bei den Serverchips auch zwischen den bis zu vier Chips im Multichipmodul sorgen. Es handelt sich dabei um ein weiterentwickeltes Hyper-Transport, wie Lisa Su und Mark Papermaster im Pressegespräch bestätigten.

Was Hans de Vries noch nicht aus den paar Pixeln herausinterpretieren konnte, ist das tiefere Innenleben eines Zen Kerns. Das wurde nun auf der Hot-Chips-Konferenz von Chefarchitekten Mike Clark entblättert. Clark hat an so gut wie allen AMD-Prozessoren seit dem K5 mitgewirkt, er war unter anderem für den Opteron Barcelona (K10) verantwortlich, dem leider mit dem TLB-Bug ein so unglückliches Schicksal beschieden war.

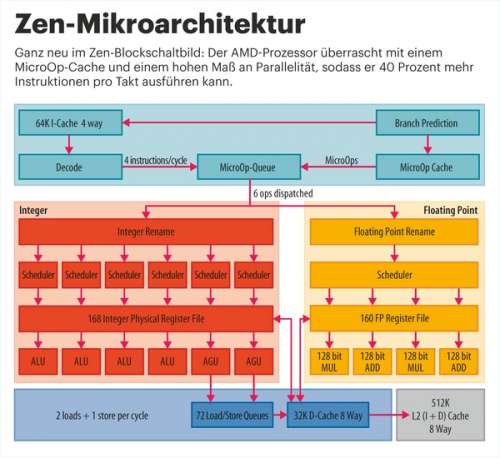

Zahlreiche Neuerungen gibt es gegenüber dem alten Bulldozer-Design. Zunächst einmal kehrt AMD wieder zu den Kernen mit eigenen Instruktionspfaden und Gleitkommaeinheiten zurück, wie sie beim älteren K8/K10 üblich waren. Dann gibt es jetzt einen MicroOp-Cache hinter den Dekodern, ähnlich wie ihn Intel mit Sandy Bridge eingeführt hatte. Und, ebenfalls inspiriert von Intel, hat man ein zweifaches simultanes Multithreading (SMT) eingeführt, das bei Intel Hyper-Threading heißt.

Weiterhin wurde die Sprungvorhersageeinheit komplett neu mit höherer Trefferquote gestaltet. Den L1-Instruktionscache hat AMD ebenfalls neu konzipiert und auf 64 KByte verdoppelt. Er enthält jetzt auch keine Predecoded Bits mehr, wie es bei früheren AMD-Designs üblich war. Der L1-Data-Cache hat seine Größe von 32 KByte behalten, ist aber jetzt wieder als Write-Back ausgeführt.

Aus der MicroOp-Queue können bis zu sechs Operationen pro Takt verteilt werden, davon können bis zu vier Gleitkommaoperationen sein. Die Integer- und Gleitkommapfade gehen wie bei AMD üblich gleich hinter der Queue getrennte Wege. Bei Integer hat man vier ALUs und zwei Adressberechnungseinheiten AGUs, die im Idealfall alle parallel arbeiten. Bei Gleitkomma sind es vier Einheiten, zweimal FPMUL, zweimal FPADD.

Der Pfad für die Ergebnisse (Retirement) kann sogar bis zu acht Ergebnisse pro Takt aufnehmen – hier ist eine Engstelle im Intel-Design, das auf maximal vier Ops/Takt limitiert ist.

Ein paar Dinge, das gab Clark im Gespräch zu, fehlen aber im Vergleich zur Konkurrenz noch, etwa ein Loop Stream Detector. Diese Einheit in Intels aktuellem Core-Design erkennt in der MicroOp-Queue kleine Schleifen, kann diese im Trefferfall schnell ausführen und während der Laufzeit das Frontend energiesparend abschalten. Das nachzureichen wäre ein Job für den Zen+. Auf diesen in Arbeit befindlichen Nachfolgechip wartet aber eine noch weit wichtigere Aufgabe, denn die Vektoreinheiten sind bei Zen bislang nur 128 Bit groß. Zwar unterstützt der Prozessor 256-bittiges AVX2, indem er zwei der doppelt vorhandenen Einheiten zusammenschaltet und er besitzt auch zwei 128-Bit-Ports im L2-Cache. Aber damit kommt er beim Fused Multiply-Add und mithin beim wichtigen Linpack-Benchmark nur auf die halbe Performance des Haswell. Und wenn im nächsten Jahr Skylake-EP mit AVX512 herauskommt, dürfte der bei gleichem Takt nahezu viermal so schnell sein.

Dafür wird AMDs Serverchip Naples mit vier Dice auf einem Multichipmodul mit seinen 128 PCIe-3.0-Lanes und 8 Speicherkanälen punkten können – und Speicherperformance wird bei Serverjobs selbst im HPC-Bereich immer mehr statt purer Rechenleistung gefordert. Hier macht inzwischen der neue Benchmark HPCG Furore, der vor allem Speicherperformance abcheckt.

Im Benchmark-Vergleich mit Blender zeigte sich Summit Ridge mit acht Kernen gegenüber dem Zehnkerner Broadwell E in etwa gleichwertig. Der Broadwell E wurde dafür auf den gleichen Takt von 3,0 GHz heruntergefahren und Turbo abgeschaltet. Er hatte zwar nur zwei der unterstützten vier Speicherkanäle bestückt, das dürfte aber beim Blender-Benchmark so gut wie keine Rolle spielen. Dass jedoch dieser Benchmark via CPUID-Abfrage auf unterschiedliche Codes verzweigt, macht die Sache aber ein wenig schräg.

Dennoch: Im Prinzip hat AMD jetzt einen Prozessor, der in etwa gleichwertig mit Haswell/Skylake ist, wenn auch mit vielen Unterschieden im Detail, mit schwächerer Vektoreinheit, aber mit größeren Caches und je nach Sichtweise höherer Skalarität. Ein „Me-too-Chip“ also, aber einer, den die Industrie und die Kunden dringend brauchen, um die Märkte wieder lebendig zu gestalten.

M1, Power9 …

Neben Zen gehörten Nvidias Parker (Seite 33), Samsungs M1 und IBMs Power9 zu den Prozessor-Highlights der Hot-Chips-Konferenz. Samsungs erster selbst entwickelter ARMv8-Prozessorkern M1 war, wie man an den üppigen Ressourcen und der hohen Speicherbandbreite erkennen kann, ursprünglich mal für Server gedacht, wurde dann aber für Mobile umgewidmet – es sieht nun so aus, als ob Samsung den einst angepeilten Servermarkt wohl gar nicht mehr ins Auge fasst. Der M1-Kern ist derweil schon im Einsatz, er wird im Exynos 8890 des Galaxy S7 verwendet. Hier arbeiten vier M1-Kerne zusammen mit vier Cortex-A53. Abgesehen von der Speicherbandbreite ist der M1 allerdings performancemäßig nicht aufregend weit von einem Cortex-A57 entfernt.

IBM hatte den Power9 schon auf dem OpenPower Summit im Mai mit seinen wichtigsten Eckdaten vorgestellt. Auf der Hot Chips folgten nun die beeindruckenden Details. Den Power9 gibt es in vier Ausführungen. Man kann wählen zwischen 24 Kernen und 4-fach SMT (SMT4) oder 12 Kernen und 8-fach-SMT (SMT8). In beiden Fällen hat man 96 Threads. Für Linux ist SMT4, für PowerVM eher SMT8 von Vorteil. Für jede Version gibt es eine für zwei Sockel gedachte Scale-Out-Variante mit acht DDR4-Kanälen oder die Scale-Up-Version für vier oder mehr Sockel mit Centaur-Memory-Bus samt L4-Cache. Eine ähnliche Aufteilung hat man bei Intel mit den EP/EX-Linien ja auch.

Die Ingenieure schafften es, die Pipeline vom Power8 um fünf Stufen auf nunmehr zwölf zu verkürzen. Die Gleitkommamöglichkeiten der vier FPUs (bei SMT4) sind jetzt noch mächtiger. Hinzugekommen ist unter anderem das Rechnen mit FP128, also mit Long-Double-Genauigkeit. Für je zwei SMT4-Kerne stehen 10 MByte L3-Cache (NUCA: Non-uniform Cache) als EDRAM zur Verfügung, also insgesamt 120 MByte. Der Power9 wird der erste Prozessor mit PCIe 4.0 sein (48 Lanes). Daneben bietet er ein Bluelink-Interface mit ebenfalls 48 Lanes, eine jede mit 25 GBit/s. Über dieses Interface wird NVlink 2.0 zum Anschluss von Nvidia-GPUs sowie das „New CAPI“ für andere Acceleratoren (ASICs/FPGAs) gespeist. Den Performance-Zuwachs gegenüber Power8 bei gleichem Takt beziffert IBM mit 80 Prozent bei Integer (SPECint_rate2006) und 55 Prozent bei Float (SPECfp_rate2006).

Lange Vektoren

Und dann gabs noch den Auftritt der beiden japanischen Firmen ARM und Fujitsu. Sie haben gemeinsam eine skalierbare Vektorerweiterung (SVE) von 128 bis 2048 Bit entwickelt, die mit einem Vektorlängen-agnostischen Programmiermodell arbeitet. Das soll bei unterschiedlich ausgestatteter Hardware keine Neukompilierung erfordern, sondern vollautomatisch skalieren. Wie bei AVX512 kann man dabei einzelne Lanes der 32 SVE-Register über ein Predicate-Register ausblenden.

SVE unterstützt Int8, Int16, Int32 und Int64 sowie FP32 und FP64. Der neue Deep-Learning-Trend mit FP16 hat sich wohl noch nicht bis Japan rumgesprochen – aber es gibt ja auch schon Algorithmen, die dafür nur Int8 nutzen. Fujitsu plant einen Prozessor für den Post-K-Computer mit 512 Bit Vektorlänge. Auf den wird man aber wohl noch bis 2020 warten müssen. (as@ct.de)