Titanische Sicherheit

Googles „OpenTitan“-Sicherheitschip mit RISC-V-Technik

Google entwickelt Sicherheitschips für Pixel-Smartphones, Chromebooks und Cloud-Server. Bei letzteren setzt man nun auf die offene CPU-Mikroarchitektur RISC-V und legt das Design offen.

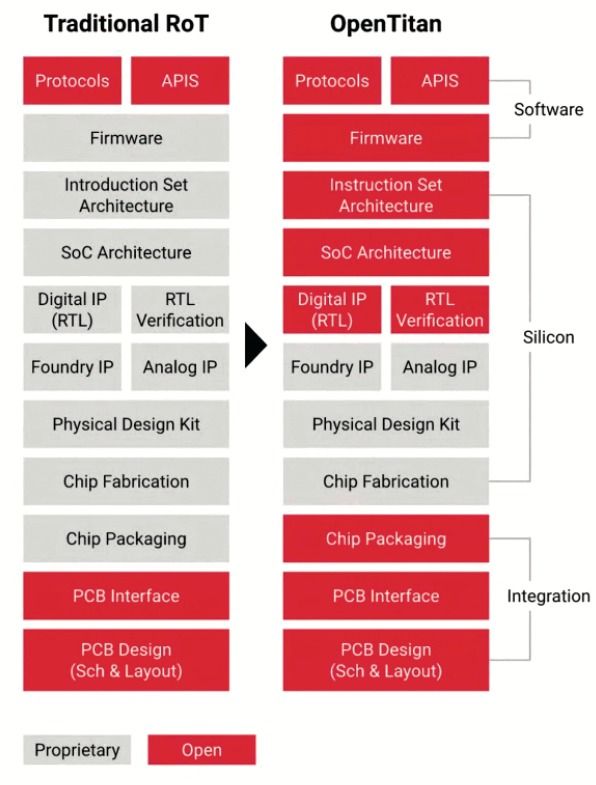

Google stattet die eigenen Cloud-Server mit selbst entwickelten „Titan“-Sicherheitschips aus, die kryptografische Zertifikate speichern und Schlüssel unabhängig vom Hauptprozessor verifizieren. Sie dienen als Hardware-Vertrauensanker (Root of Trust, RoT) beim Fernzugriff und schützen Firmware vor Manipulationen. Um das Vertrauen von Cloud-Kunden zu stärken, entwickelt Google jetzt in einer offenen Partnerschaft OpenTitan-Chips, deren Design und Firmware offen liegt. Dadurch können andere Firmen verifizieren, dass keine Hintertüren eingebaut sind. Google legt die OpenTitan-Verantwortung in die Hände des britischen RISC-V-Spezialisten lowRISC; zu den ersten Partnern gehören der SmartCard- und SIM-Experte Giesecke & Devrient sowie Western Digital (WD). Der Mikrocontroller-Kern Ibex wurde an der ETH Zürich entwickelt und erfüllt die RISC-V-Spezifikation RV32IMC.

WD will OpenTitan künftig in sicheren Speichersystemen nutzen, Google zunächst für Cloud-Server. In Zukunft kann OpenTitan aber auch in Smartphones zum Einsatz kommen oder in FIDO2-Dongles für die Zwei-Faktor-Authentifizierung an PCs und Notebooks. Googles bisherige Titan-Versionen H1 für Chromebooks und im Titan M von Pixel 3 und 4 arbeiten mit ARM-Kernen. Die „Titan-Sicherheitsschlüssel“ mit USB, NFC und Bluetooth stammen wiederum von Yubico oder Feitian; darin stecken Sicherheitschips etwa von Infineon oder STMicroelectronics. Nur die Firmware programmiert Google selbst.