Prozessorgeflüster

Von Multi Core und Multi Beam

Google gibt endlich Details über die Tensor Processing Unit bekannt und Intel weitere Interna zum 10-nm-Prozess – und wie man mit Hyper Scaling das Mooresche Gesetz rettet.

Nun weiß man etwas mehr über die Hardware namens Tensor Processing Unit (TPU), mit deren Hilfe vor einem Jahr der Top-Profi Lee Seedol zu dessen großem Erstaunen im Go-Turnier besiegt wurde. Die Google-Entwickler verwendeten für ihr neuronales Netz nicht etwa 32 oder 16 Bit Gleitkomma, sondern 8 Bit Integer – und davon gleich 65.536 Einheiten. Eine jede kann eine Multiplikation und Addition (MAC) in einem Schritt ausführen. Diese MAC-Operation ist das Herzstück der Matrixmultiplikation, die ihrerseits die Grundfunktion des Algorithmus für das Training von neuronalen Netzen bildet.

Bei 700 MHz Takt kommt Googles TPU mit Int8 auf 91,7 Tops/s, etwas mehr als das Doppelte einer Tesla P40. Googles Studie dazu ist allerdings schon etwas betagt und vergleicht die TPU mit Intels Haswell und Nvidias Tesla K80. In diesem Feld konnte sich die TPU mit 13- bis 15-fach höherer Performance gegenüber der K80 und dank nur 75 Watt TDP mit bis zu 25- bis 30-facher Energieeffizienz auszeichnen (bezogen allein auf die Karte, ohne Host-System). Der Haswell war dann noch mal Faktor 2 bis 3 langsamer.

Natürlich sähe der Vergleich zu einer aktuellen Tesla P40 recht anders aus, allerdings weist Google darauf hin, dass man damals noch DDR3 verwendet habe – mit dem GDDR5 der modernen GPUs wäre jetzt die Performance der TPU bei den üblichen Algorithmen dreimal so hoch. Außerdem wurde die TPU noch im 28-nm-Prozess hergestellt, von wem auch immer – über Hersteller und Die-Größe gab Google keine Auskunft.

Vielleicht wär ja die nächste TPU-Version was für Intels 14- oder gar 10-nm-Prozess – an zahlreichen Chips für neuronale Netze arbeiten die Kalifornier mit ihren eingekauften Töchtern ja ohnehin.

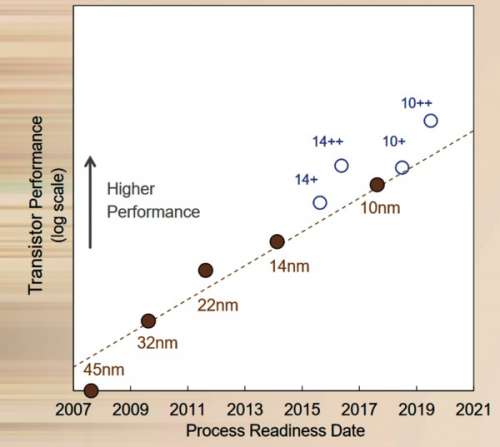

Mit ihrem 10-nm-Prozess ist Intel aber etwas in Erklärungsnot geraten. Schon auf dem letzten IDF im August 2016 hat Herstellungsleiter Mark Bohr unmissverständlich klar gemacht, dass Intels 10-nm-FinFet-Prozess ganz andere Eckdaten aufweist als die ebenfalls mit 10 nm verzierten Prozesse der Konkurrenten, die zeitlich weit voraus scheinen. Aber die Gatterabstände und SRAM-Zellgrößen bei deren Prozessen seien deutlich größer, so Bohr. Jetzt hat Intel das noch einmal auf einem speziellen „Manufacturing Day“ in San Francisco bekräftigt und eine neu angepasste Interpretation des Mooreschen Gesetzes nachgeliefert, die mit dem Begriff Hyper Scaling ausgedrückt werden soll. Eine Verdoppelung der Zahl der logischen Transistoren von einem Technologieknoten zum nächsten? Ja, aber nun nicht mehr im Zweijahres-Rhythmus. Das alte Tick-Tock-Modell gibts nicht mehr, nur noch Ticks mit diversen +- und ++-Zwischenstufen.

Allerdings soll dabei die Rate der allgemeinen Transistordichte und die der Kosten pro Transistor weiterhin mit dem klassischen Moore’s Law verlaufen – das soll ja schließlich irgendwie weiterleben.

Maskenschreiber

Um sich hier zukünftige Wege abzusichern, hat sich Intel Mitte letzten Jahres recht stiekum für rund 135 Millionen Euro die Wiener Firma IMS Nanofabrications zu gut 96 Prozent einverleibt. Diese Österreicher entwickeln Nanoschreiber für lithografische Masken mit Elektronen und Ionenstrahlen, sogenannte Multi Beam Mask Writer (MBMW). Bis zu 1,5 Millionen Elektronenstrahlen mit 50 kEV werden hier parallel angesteuert, um die für die Volumenproduktion nötige Schreibgeschwindigkeit zu erzielen. Seit Februar arbeitet IMS mit der japanischen Firma JEOL zusammen, gemeinsam will man den weltweit ersten produktionstauglichen Multi-Beam-Maskenschreiber herausbringen. Ziel sind Masken für 10 nm und später auch darunter.

Besonders spannend dürfte für Intel insbesondere die bei IMS ebenfalls in der Forschung befindliche Direct-Write-Technik sein, bei der die Elektronenstrahlen ohne lithografische Masken direkt die Layer auf dem Wafer „gravieren“. Etwa 200-mal mehr parallele Elektronenstrahlen wären für solche Anlagen in der Volumenfertigung nötig, aber womöglich schafft man das eher als zuverlässig funktionierende EUV-Belichter. Gut möglich, dass Intel für 7 nm schon auf Direct Write schielt, notfalls, so hat Bohr bereits auf dem IDF verkündet, habe man auch noch einen 7-nm-Prozess mit klassischer 193-nm-Laserlithografie mit weiterentwickelter Multi-Pattern-Belichtung in petto, um auf jedem Fall das Mooresche Gesetz, sorry, das Hyper Scaling lebendig zu halten.

Zu Gerüchten, der 10-nm-Prozess habe weiterhin mit großen Ausbeuteproblemen zu kämpfen, äußerte sich Intel wie üblich nicht, jedenfalls nicht öffentlich. Aber zuletzt beim Treffen der SPIE (Society of Photographic Instrumentation Engineers) Anfang März klang durch, dass die Ausbeute in der Volumenproduktion klar unter den Erwartungen liege. Das könnte weitere Verzögerungen von zwei, drei Monaten bedeuten.

Auch wenn Intel angibt, man sei „on tack“ für die Herstellung in der zweiten Jahreshälfte, größere Chips wird man in der ersten Cannon-Lake-10-nm-Generation wohl kaum begrüßen dürfen. Zunächst haben nur die winzigen Mobile-Chips der U- und Y-Klasse genügend Ausbeute. In der nackten Transistorperformance ist der 10-nm-Prozess dem optimierten 14++-nm-Prozess zudem nicht mal überlegen. Wie Intel auf dem Manufacturing Day in einer Folie offen zugab, kommt erst der 10+-nm-Prozess in etwa auf das Niveau … Die Sechskern-Desktop-Prozessoren fertigt Intel dann doch lieber erst mal im 14++-nm-Prozess.

Es gilt überdies als sicher, dass die Cannon-Lake-Xeons ganz gecancelt sind. Analysten haben schon ausgerechnet, dass für sie das sinnvolle Zeitfenster zu klein wäre, allenfalls Embedded-Versionen als Nachfolger vom Xeon-D kämen in Frage. Ansonsten wird man wohl auf Ice-Lake-EP in 10+nm warten müssen – und das bis mindestens 2019. Nebenbei stellt sich auch die Frage nach dem besonders großen 88-Kerner Xeon Phi Knights Hill. Wird er wirklich weiterhin für den offenbar wenig performanten und mit der Ausbeute kämpfenden 10-nm-Prozess designt oder verschiebt man auch ihn für 10+? Sicherheitshalber kauft Intel für alle Fälle schon mal diverse, relevante Hardwarefirmen mit anderen Prozessorarchitekturen auf, erst Altera für 16,7 Milliarden Dollar (8-facher Jahresumsatz) mit ARM64-Chips im Stratix-10, im Herbst dann das kleine Start-up Nerwana für 408 Millionen (ohne Umsatz) mit selbst entwickeltem Lake-Crest-Chip und nun im März Mobileye für 15,3 Milliarden (40-facher Jahresumsatz) mit Mips-I6500-Warrier-SoCs. Mithilfe von Intel und den Kameras von Mobileye will ja vor allem BMW Spitzenreiter in der Formel 1 des autonomen Fahrens werden. (as@ct.de)