Petabytes für Server

Neue SSDs und Flash-Alternativen auf dem Flash Memory Summit

Mehr, schneller, billiger: Ein neues SSD-Format zielt auf Petabyte-Speichersysteme und Gen-Z-Server bringen eine neue Systemarchitektur. Flash-Alternativen wie ReRAM und 3D XPoint kommen nur langsam auf Touren.

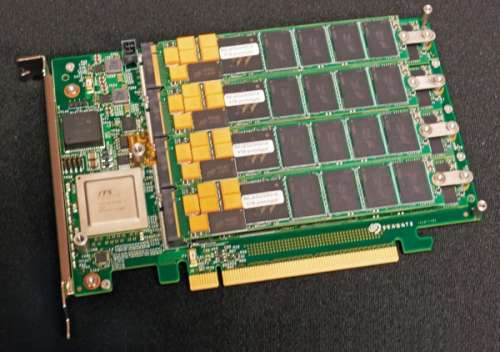

NAND-Flash-Speicherchips knacken die 1-Terabit-Marke, damit bestückte SSDs sollen 128 TByte fassen: mehr als das Zehnfache der größten Festplatten. Zwar verzögern sich die vollmundig angekündigten Riesen-SSDs oft um mehrere Monate, aber die Richtung ist klar. So liefert Seagate die im vergangenen Jahr auf dem Flash Memory Summit gezeigte 60-TByte-SSD wohl noch immer nicht in großen Stückzahlen, brachte nun aber eine neue Technologiestudie mit: eine PCI-Express-SSD mit 64 TByte. Auf der Karte sitzen 8 M.2-SSDs mit je 8 TByte aus 3D-NAND-Flash-Chips von Micron. Beim sequenziellen Lesen verspricht Seagate-Manager Kent Smith 13 GByte/s: Das sei nah am Limit dessen, was mit 16 PCIe-3.0-Lanes möglich ist.

Für eine SSD mit 128 TByte bringt Samsung das hauseigene V-NAND in der fünften Generation auf 1 Terabit pro Die. Diesmal sind nicht mehr Lagen geplant, sondern mehr Bits pro Zelle: Jede Quadruple Level Cell (QLC) speichert vier Bits statt nur drei (TLC) oder zwei (MLC). Samsung plant Flash-Chips mit 2 TByte: 16 gestapelte Dies zu je 1 TBit. Zur Haltbarkeit des Speichers gab es keine Angaben, aber sie dürfte etwas unter der von TLC-Speicher liegen – die riesige Kapazität und verbesserte Controller-Algorithmen gleichen etwas niedrigere „Endurance“-Werte der einzelnen Zelle aus. Die nächste Version der SAS-SSD PM1643 soll als erste mit diesem Speicher ausgestattet sein, dürfte jedoch erst 2018 erscheinen.

Ebenfalls mit Serial Attached SCSI, sogar mit MultLink SAS, kommt Toshibas PM5 mit bis zu 30,72 TByte im „dicken“ 2,5-Zoll-Format. Für MultiLink SAS bündelt der SSD-Controller vier SAS-12G-Kanäle; der Steckverbinder bleibt bei SFF-8639, erhält aber mehr Kontakte. Beim Lesen soll die PM5 bis zu 3,35 GByte/s erreichen, beim Schreiben 2,72 GByte/s.

Das NVMe-Schwestermodell CM5 mit maximal 18,36 TByte hat einen Dual-Port-NVMe-Controller. Dual-Porting lässt sich für höhere Zuverlässigkeit nutzen, aber auch für mehr Durchsatz durch Parallelbetrieb. Die CM5 bringt vor allem mehr Zugriffe pro Sekunde (IOPS).

Gleich drei verschiedene Versionen der Server-SSD 9200 präsentierte Micron. Die Eco-Version ist für Lesevorgänge optimiert, die Max-Version für hohe Schreiblast und das Pro-Modell steht dazwischen. Alle sind als PCIe-Karte im Server-Format (halbe Höhe, halbe Länge: HHHL) sowie als U.2-Version erhältlich. Während es die Eco-Version mit 8 und 11 TByte gibt, bringt es die Max auf maximal 6,4 TByte. Bei den Zugriffen auf zufällige Adressen gibt Micron für alle Varianten beim Lesen bis zu 1 Million IOPS an, beim Schreiben sind es maximal 700.000. Sequenzielle Zugriffe verarbeiten die Laufwerke mit bis zu 4,6 GByte/s beim Lesen, beim Schreiben sind es maximal 3,8 GByte/s.

SSD-„Lineale“

SSDs im 2,5-Zoll-Gehäuse oder als M.2-Streifen nutzen den Platz in einem Servergehäuse nicht optimal aus. Die neue Bauform „Ruler“ (Lineal) verspricht bis zu 1 Petabyte (PByte) in einem einzigen Rack-Einschub mit 4,45 Zentimetern Bauhöhe, also einer Höheneinheit (HE). Intel arbeitet dabei unter anderem mit Samsung und Facebook in der dazu gegründeten Gruppe Enterprise & Datacenter Storage Form Factor (EDSFF) zusammen.

Die SSD-Module sind 9,5 Millimeter flache, aber 32,535 cm lange Riegel mit 3,68 cm Höhe. Zur Belüftung bleibt zwischen den Modulen je 3 Millimeter Platz. So passen 32 Ruler-SSDs in ein 1-HE-Gehäuse; sie lassen sich im laufenden Betrieb austauschen und stecken auf einer Backplane. Dahinter bleibt Platz für zwei Xeons samt Chipsatz und RAM.

Jede Ruler-SSD ist mit 4 oder 8 PCIe-Lanes angebunden, doppelt hohe Versionen für 16 PCIe-Lanes sind möglich. Auch PCIe 4.0 und sogar PCIe 5.0 werden künftig unterstützt. Erste Ruler-SSDs mit bis zu 16 TByte will Intel zum Jahresende fertigen. Als Basis dient die DC P4500 mit 3D-Flash aus der Gemeinschaftsproduktion mit Micron. Laut Intel ist lediglich das Platinenlayout neu, dazu kämen minimale Änderungen der Firmware. 2018 sollen Ruler-SSDs mit 32 TByte kommen, damit werden 1024 TByte auf 1 HE möglich.

MRAM und ReRAM

Ebenfalls als Technologiedemonstration zeigte Seagate eine SSD mit 128 MByte MRAM für Meta-Informationen: Der schnelle, nichtflüchtige Speicher soll die Geschwindigkeit steigern. Bisherige SSDs schreiben diese Daten in ihren langsamen Flash-Speicher. Kurz vor dem Flash Memory Summit hatte Everspin gemeldet, nun auch MRAM mit 1 GBit (128 MByte) pro Chip auszuliefern – bisher waren es höchstens 256 MBit. Doch auch mit 1 GBit hat MRAM viel zu wenig Kapazität, um mit NAND-Flash konkurrieren zu können.

ReRAM kommt schon dichter heran, auch weil ReRAM-Entwickler Crossbar den Fertigungsprozess auf rund 20 Nanometer schrumpfen konnte: 8 GBit pro Chip sollen damit möglich werden. Doch auch das ist weit von Flash entfernt und ReRAM ist damit nur für Einsatzbereiche interessant, wo die spezifischen Vorteile zum Tragen kommen, etwa der niedrige Energiebedarf beim Schreiben.

Intels 3D XPoint, die Flash-Alternative hinter Optane und Micron QuantX, spielte keine große Rolle auf dem Flash Memory Summit – kein Wunder nach den ganzen Verzögerungen. Bill Leszinske von Intels NVM Solutions Group gab sich im Gespräch mit c’t jedoch zufrieden: Die Optane-Fertigung laufe auf Hochtouren. Derzeit konzentriere man sich mit der SSD DC 4800X auf das Rechenzentrumsgeschäft – und 3D XPoint soll auch im Ruler-Format kommen.

In verschiedenen Vorträgen und Diskussionen waren sich die Sprecher aber einig: NAND-Flash wird noch zwei oder drei Entwicklungsschritte machen und mindestens bis 2023 weiter dominieren. Die anderen Techniken werden sich zwar in Nischen etablieren, aber Flash nicht allgemein ablösen. Der Flash-Preis pro Bit soll in den kommenden Jahren weiter stark fallen, ein Analyst schätzte 75 Prozent in den kommenden sechs Jahren.

Neue Systemarchitektur

Das Konzept aktueller Server ist veraltet, sagt Kurtis Bowman, Dell-Manager und Vorsitzender des Industriegremiums Gen-Z. Solle etwa die Grafikkarte etwas berechnen, müssten die Daten erst einmal von der CPU dorthin und nach der Berechnung wieder zur CPU zurückübertragen werden.

Das Konsortium Gen-Z erarbeitet Spezifikationen für eine neue Server-Architektur, bei der Speicher im Zentrum steht. Bei Gen-Z-Maschinen greifen CPU und Grafikkarte auf gemeinsame Speicherbereiche zu, was Datentransfers vermeidet, die Zeit und Energie schlucken. Als Speicher kommt dabei nicht nur DRAM in Betracht, sondern auch Storage Class Memory wie 3D XPoint oder Samsungs Z-SSD – und dieser Speicher darf auch extern angebunden sein.

Die erste Version des Gen-Z-Standards soll Ende des Jahres stehen. Bis zum Erscheinen erster Hardware dürfte dann noch mindestens ein Jahr vergehen, sagte Bowman. Intel ist zwar nicht im Gen-Z-Konsortium vertreten, Bowman zeigte sich aber überzeugt, dass man dort sehr genau über die Fortschritte informiert sei. Gen-Z zielt schließlich auf Intel-Konzepte wie die Omni-Path Architecture (OPA) mit 100 GBit/s und Ansätze für „disintegrated“ Server mit optischen PCIe-Interconnects.

Neue Ideen gibt es aber auch bei NVMe-SSDs: Samsung erwähnte einen Ansatz für Key-Value-Stores ohne Nachteile der blockweisen Verwaltung – das geht in Richtung Object Storage. Toshiba erwähnte bei der CM5, dass sich deren internes DRAM mit neuen NVMe-Funktionen etwa auch für Journaling-Funktionen von Datenbanken nutzen ließe. Das wäre billiger und weniger aufwendig als der Einsatz teurer NVDIMMs. NVMe-over-Fabrics (NVMeF) ermöglicht solche Persistent Memory Regions mit Funktionen wie Scatter-Gather List (SGL) und Controller Memory Buffer (CMB). (ll@ct.de)