FPGA-Prozessorkerne leichter programmieren

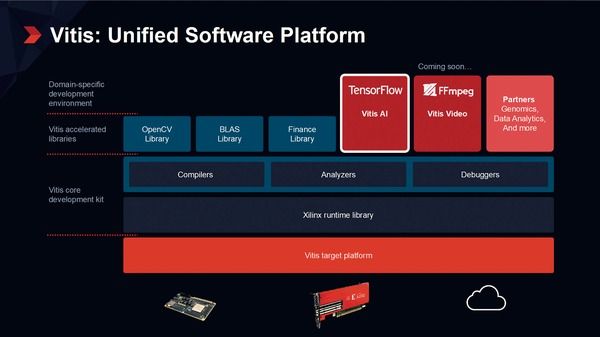

Zur Programmierung programmierbarer Logikchips, sogenannter Field Programmable Gate Arrays (FPGAs), sind oft komplizierte und teure Entwicklungsumgebungen nötig. Xilinx will das ändern: Die Vitis Unified Software Platform ist für C, C++ oder Python ausgelegt, unterstützt Standard-Frameworks wie TensorFlow und Caffe für KI, lässt sich in IDEs wie Eclipse einbinden und bringt optimierte Bibliotheken für gängige Aufgaben sowie FPGA-Treiber mit.