Moore’s Law lebt

Halbleiter-Trends und neue High-End-Chips

Der Forschungschef des Chip-Auftragfertigers TSMC skizziert auf dem Hot Chips Symposium die Zukunft der Halbleiterindustrie. Und ein Riesen-Chip für künstliche Intelligenz nutzt fast einen ganzen Wafer.

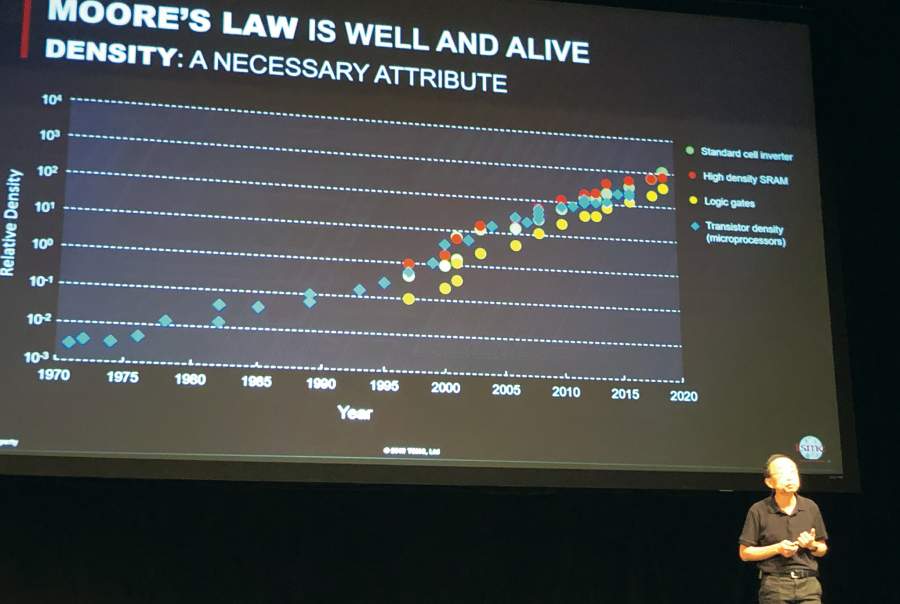

Geht es nach Philip Wong, Forschungschef des weltgrößten Chip-Auftragsfertigers TSMC, dann gilt das Moore’sche Gesetz auch noch im Jahr 2050. Die Metrik, die Wong für seine Aussage nutzt, ist die Packdichte der Transistoren. In der Vergangenheit war die Strukturbreite die gängige Stellschraube für immer dichter gepackte Transistoren, und an ihr werde man in absehbarer Zeit auch weiterhin drehen. 5-nm-Chips seien bereits als Prototypen verfügbar und danach werde es feinere Fertigungsprozesse geben.

Wenn die Strukturgrößen in den Bereich weniger Atomlagen schrumpfen, verändert sich allerdings das Verhalten bisheriger Transistortypen zum Schlechteren. Bislang noch nicht verwendete Materialien wie MoS2, WSe2 oder WS2 zeigen hingegen auch bei Dicken von einem Nanometer und darunter noch gute Resultate. Auch an den schon länger bekannten Kohlenstoffnanoröhrchen wird weiterhin viel geforscht. Zusätzlich kämen weitere Verbesserungen hinzu. Als aktuelles Beispiel nannte Wong FinFETs, also dreidimensionale (Gate-)Strukturen auf dem Wafer.

Den aktuellen Trend, statt großer monolithischer Dies mehrere kleinere Chiplets zu einem großen Ganzen zusammenzuschalten – wie AMD es beispielsweise bei den jüngst erschienenen Zen-2-CPUs tut –, sieht Wong als einen weiteren Kniff. Die Idee sei aber alles andere als neu: Auf Seite 3 von Gordon Moores berühmter Veröffentlichung anno 1965 findet man die Bemerkung, dass es mitunter sinnvoll sein könne, große Systeme aus kleineren Funktionseinheiten zusammenzusetzen.