Prozessorgeflüster

Von Nusskuchen und Mandelbrot

Harte Nuss für Intel: Den Servermarkt beherrscht man nicht mehr nach Belieben. Allein Microsoft unterstützt gleich vier verschiedene Open-Compute-Plattformen für x86 und ARM, inklusive des AMD-Prozessors Naples.

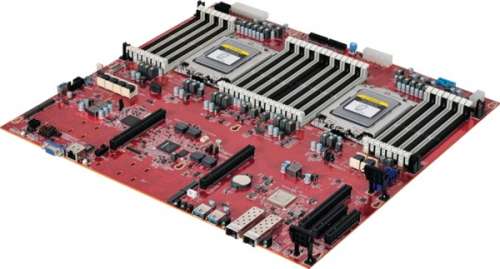

Microsoft überraschte auf dem OpenCompute Summit in Santa Clara weniger mit dem Olympus-System für Skylake-EP – das hatten die Redmonder in Grundzügen schon im November letzten Jahres vorgestellt – als vielmehr mit den beiden Varianten für ARM64 mit Cavium Thunder X2 und Qualcomm Centriq 2400 „Amberwing“ sowie mit einer Plattform für AMDs geplanten Serverprozessor Naples (siehe auch S. 22). Auch für ARM64 wird es Windows Server geben, vorerst allerdings nur in der Cloud. Am Scheduler für Windows 10 beziehungsweise Windows Server 2016 muss Microsoft wohl noch arbeiten, da scheint es zumindest beim AMD Ryzen derzeit noch zu haken.

Daneben konnte man auf dem Summit die OpenPower-Plattform Zaius für Power9 bewundern, designt von Google, Rackspace und Partnern. Während diese mit IBMs 24-Kerner aber erst im nächsten Jahr spruchreif sein dürfte, kann man mit etwas Glück zumindest drei der vier genannten Konkurrenten schon Mitte des Jahres begrüßen.

Um den heißen Wettbewerb auf dem Servermarkt jetzt schon mal kräftig anzuheizen, gab AMD auf dem Summit erste beeindruckende Benchmarkergebnisse des 32-Kerners Naples bekannt. Danach hängt er Intels aktuelles Flaggschiff Xeon E5-2699Av4 bei speicherlastigen Aufgaben um bis hin zu Faktor 2,5 ab.

Okay, der Benchmark mit sogenannten Sparse-Matrix-Operationen war gut ausgesucht und adressiert die Sahneseite des neuen Server-Prozessors mit seinen acht DDR4-Speicherkanälen pro Prozessor, mithin mit theoretisch 170 GByte/s-Speicherbandbreite. Im Vergleich dazu nehmen sich die knapp 77 GByte/s des Xeons doch recht bescheiden aus. Hinzu kommt, dass man bei größeren Workloads in Zweisockelsystemen mit 16 DIMMs (üblicherweise 16 GByte) nicht unbedingt auskommt und man beim Xeon-System dann drei solcher DIMMs pro Channel (DPC) bestücken muss. Doch mit drei DPC sinkt die Speicherperformance noch mal um rund 20 Prozent. Und klar, just solche Workloads hat AMD ausgesucht – vielleicht hätte man zusätzlich wenigstens ein Szenario mit kleinerer Workload wählen sollen. Aber auch dann wäre der Vorsprung deutlich gewesen. Im Sommer muss sich jedoch Naples mit dem Skylake-SP mit sechs Speicherkanälen und mit bis zu 28 Kernen messen.

Wundern Sie sich dabei über das Kürzel SP (Scalable Performance) hinter Skylake? An dieses samt weiteren angehängten Endungen wie F (für Fabric OmniPath) und P (für FPGA) wird man sich jetzt wohl gewöhnen müssen. Die frühere Aufteilung in EP und EX wirds hinfort nicht mehr geben, da die zwei- und mehrsockeltauglichen Prozessoren in den gleichen 3647-poligen Sockel P3 passen. Voriges Jahr schon hatte Intel auf der ISC16 hinter den Kulissen angekündigt, „Regale“ mit vier Fächern einzuführen, die jetzt durch die hübscheren Wertbezeichnungen Platinum (81xx, 20 bis 28 Kerne), Gold (61xx/51xx, 16 bis 18 Kerne), Silver (41xx, 10 Kerne) und Bronze (31xx, weniger als 10 Kerne) ersetzt werden.

Die größeren ab Gold 61xx besitzen drei Links mit dem QPI-Nachfolger UPI mit 10,4 GT/s. Spitzenmodell ist der Xeon Platinum 8180 mit 28 Kernen, 2,5 GHz Takt, Turbo bis 3,8 GHz (AVX-Takt noch unbekannt), mit 38,5 MByte L3-Cache und einer TDP von 205 Watt. Wie viele Sockel die jeweiligen Skylake-SP-Versionen unterstützen, ist noch unklar.

AVX512-Apfelmännchen

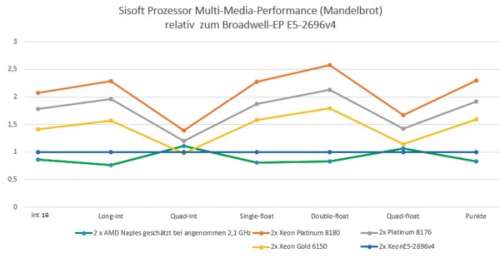

Kurz nach der Bekanntgabe der ersten Benchmarkergebnisse für AMDs Naples tauchten ganz zufällig diverse Skylake-SP-Ergebnisse auf Sisofts Ranking-Liste für „Prozessor Multi-Media-Leistung“ auf. Die Spitze übernahm mit 5836 MPix/s souverän ein Platinum-8180-System vor dem etwas niedriger getakteten Platinum 8176 mit 2,1/3,8 GHz Takt. Weiter hinten folgte der 18-Kerner Gold 6150 mit 2,7/3,7 GHz. Vorher schon fand man hier als „Core i3/i5/i7“ getarnte Prototypen mit bis zu 28 Kernen. Das Platinum-8180-System hängt dabei bei nur 492 Watt das hier gewählte Vergleichssystem mit Broadwell-EP (2696v4 mit 22 Kernen, 2,2 GHz Takt) dank AVX512 um Faktor 2,3 weit stärker ab, als es allein den etwa 45 Prozent Zuwachs durch den höheren Grundtakt und der größeren Kernzahl entspricht.

Der verwendete Sisoft-Benchmark ist übrigens nichts anders als das gute alte Apfelmännchen (Mandelbrot-Fraktal). Er bestimmt also in einer winzigen Schleife die reine SIMD-Rechenleistung für Addition und Multiplikation ohne jegliche Speicher- oder Cache-Belastung, und skaliert so üblicherweise komplett linear mit der Zahl der Kerne und dem Volllasttakt. Bei treffsicherer Schätzung des Naples-Taktes lässt sich aus den gemessenen Ryzen-Werten (518 MPix/s bei 4,09 GHz) somit ein Naples-System in dieser Disziplin recht genau einstufen. Bei angenommenen 2,1 GHz müsste es im Endergebnis etwa 17 Prozent unter dem Broadwell-EP liegen. Die nur halbe Breite der AVX-Einheiten gleicht Naples durch seine Übermacht an Kernen fast wieder aus.

Von dem unbekannten Einreicher wurde natürlich bewusst Sisofts Sandra 2.20 gewählt, denn das verwendet bereits AVX512, wo dann die Skylake-Prozessoren glänzend dastehen. Das zeigt sich insbesondere bei doppeltgenauen Gleitkommaberechnungen, bei denen das Flaggschiff gegenüber dem Broadwell-EP gar um den beeindruckenden Faktor 2,6 in Front liegt – damit kann man gleich schon mal den Linpack-Wert des 8180-Prozessorgespanns auf etwa 4,4 TFlops hochrechnen.

Höhere Genauigkeiten in „quad float“ müssen allerdings mühsam skalar zusammengerechnet werden, da bringt AVX512 nichts ein. An den Einzelergebnissen sieht man auch, dass 64-bittiges Integer weiterhin ein Mauerblümchen von AVX bleibt. Schon bei AVX256 sucht man gepackte Multiplikationen für 64-Bit-Integer vergeblich und unter AVX512 sieht das offenbar noch schlechter aus. Wo jedoch ohne viel SIMD gerechnet wird, kann Naples gut aufholen. Zur Ehrenrettung von AVX512 sei jedoch hinzugefügt, dass es hier immerhin eine gepackte 52-bittige Integer-Multiplikation gibt. Aber für sowas Ungewöhnliches gibts noch keine Benchmarks … (as@ct.de)