Vega voraus

Erste Details über AMDs neue Vega-Architektur

Kommende Grafikkarten mit Vega-GPUs sollen rasend schnell sein und den Anforderungen von Gamern, Entwicklern und Deep-Learning-Anwendungen genügen. AMD setzt auf eine verbesserte GCN-Architektur; Vega nutzt als erster Grafikchip den Hochgeschwindigkeitsspeicher HBM2.

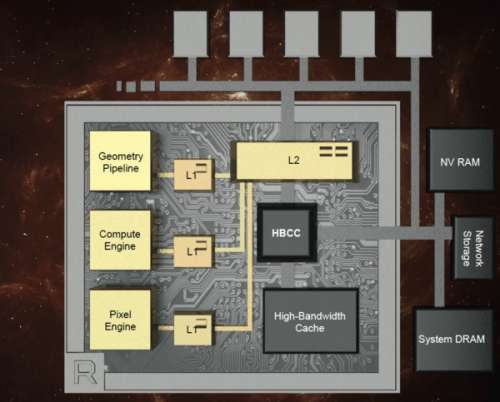

Die nächste Generation der Grafikchips von AMD hört auf den Namen „Vega“ und soll im ersten Halbjahr 2017 auf Radeon-Grafikkarten erscheinen. AMD motzt für Vega die bisherige GCN-Architektur (Graphics Core Next) an entscheidenden Stellen kräftig auf und will dadurch Spieler und Profis gleichermaßen beglücken. Dabei sollen Vega-Grafikkarten in der Lage sein, besonders große Datenmengen geschwind zu verarbeiten, die Bildqualität von Spielen und 3D-Anwendungen zu erhöhen und Supercomputing-Berechnungen schnell und effizient durchzuführen. Dafür hat AMD das Speicherinterface, die Geometrie-Pipeline, die Compute Engine und die Pixel Engine umgekrempelt.

Hochgeschwindigkeitstransfer

Um besonders hohe Transferraten zu erreichen, setzt AMD bei Vega auf High Bandwidth Memory der zweiten Generation (HBM2). Im Unterschied zu HBM1, das etwa bei der Radeon-Fury-Serie zum Einsatz kam, bietet HBM2 theoretisch die doppelte Datentransferrate – also bis zu 1 TByte/s. Die tatsächliche Transferrate von Vega ist bis dato unbekannt und hängt auch davon ab, wie viele Speicher-Stacks AMD einsetzt – Gerüchten zufolge sollen es in der Consumer-Version zwei mit jeweils 8 GByte Fassungsvermögen sein, die mit 512 GByte/s arbeiten. Das wäre dann nur so schnell wie eine Radeon R9 Fury X mit HBM1 – deren Flaschenhals war allerdings nicht die Transferrate, sondern die Videospeichergröße von nur 4 GByte und die Rechenleistung des Fiji-Grafikchips.

Feinheiten über die Speicherhierarchie ihrer GPUs geben weder AMD noch Nvidia heraus. Mit welchen Bandbreiten, Latenzen und Assoziativitäten die Caches arbeiten und wie das mit der Virtualisierung und den Translation Lookaside Buffers (TLBs) aussieht – diese offenen Fragen versuchen Wissenschaftler mühevoll mit Microbenchmarks herauszutüfteln. Bislang liegen Ergebnisse für Nvidia Fermi, Kepler und Maxwell (mit zwei TLB-Leveln) vor. AMD spricht bei Vega von einem revolutionären High Bandwidth Cache Controller (HBCC). Er soll im Zusammenspiel mit einem speziellen High Bandwidth Cache „adaptive feinkörnige Datenbewegungen“ ermöglichen. Dazu gehört insbesondere das Paging auf externe Speicher, etwa Arbeitsspeicher, SSDs, NVRAM und Netzwerkspeicher. Anwendungen lässt sich dadurch ein besonders großer Videospeicher vorgaukeln. Der zur Verfügung stehende virtuelle Adressraum soll 512 TByte (48 Bit) betragen – so wie übrigens bei Nvidia Pascal auch.

Der HBCC dürfte mit nicht weiter spezifizierten TLBs zusammenarbeiten, die wie bei den CPUs üblich nicht schon bei der Allokation, sondern erst beim tatsächlichen Zugriff den physischen Speicher zuordnen. Häufig allokieren nämlich Spiele wesentlich mehr Videospeicher, als sie tatsächlich verwenden. Mit Vega lässt sich nun der Videospeicher effizienter nutzen.

Durch die neue programmierbare Geometrie-Pipeline mit Primitive-Shader-Stages soll Vega einen doppelt so hohen Polygondurchsatz wie bisherige Radeon-GPUs erreichen. Das kommt insbesondere geometrielastigen Spielen zu Gute, wie derzeit etwa Deus Ex Mankind Divided. Durch verbesserte Verteiler (Intelligent Workgroup Distributor) will AMD die Geometrie-, Compute- und Pixel-Engines besser auslasten. Seine Pixel Engine hat AMD an einem wichtigen Punkt überarbeitet: So sind die Render Backends nun direkt mit dem L2-Cache verbunden (statt wie bisher über den Speicher-Controller), wodurch die GPU besonders bei Deferred-Shading-Anwendungen eine höhere Leistung entfalten soll.

Ferner soll Vega ein verbessertes Load Balancing aufweisen. Das ist ein vielschichtiger Begiff, der insbesondere im Zusammenspiel von mehreren GPUs mit OpenGL, Vulcan oder DirectX 12 (Multiadapter) interessant ist – auch mit heterogener Lastverteilung zwischen GPU und CPU. OpenCL 2.0 bietet mit den Pipes die Möglichkeit, mehrere Kernel auf einer GPU zu balancieren, ähnlich wie Hyper-Q oder Cuda-proxy bei Nvidia.

Next-Gen Compute Units

Die Organisation von Funktionseinheiten wie Shader-Rechenkernen in Arbeitsgruppen behält AMD bei, nennt sie aber nun nicht mehr Compute Units (CU), sondern Next-Gen Compute Units (NCU). Die erste Grafikkarte mit Vega-10-GPU soll 64 NCUs mit jeweils 64 Shader-Rechenkernen enthalten. Diese sollen nun auch besonders hohe Taktfrequenzen mitmachen (ähnlich wie Nvidia sie bei Pascal-GPUs fährt) und das mit mehr Instruktionen pro Takt (IPC).

Vor allem soll die Vega-NCU doppelt so viele fp16-Operationen pro Takt ausführen (wie Nvidias High-End-GPU GP100) wie fp32, nämlich 256 statt 128. Dadurch will AMD bei der lukrativen Deep-Learning-Industrie mitspielen, in der Nvidia schon seit einigen Jahren aktiv ist. Auch 8-Bit-Integer kommt hier in Mode, davon beherrscht Vega dann 512 pro Takt und NCU.

Die früheren AMD-GPU-Generationen seit Hawaii kannten fp16 zwar als platzsparendes Datenformat, konnten Berechnungen aber nur mit der gleichen Performance wie Single Precision ausführen. Wie es mit der Performance bei doppelter Genauigkeit aussieht – da muss man sich überraschen lassen, denn die soll in noch unbekannten Bereichen konfigurierbar sein. (mfi@ct.de)